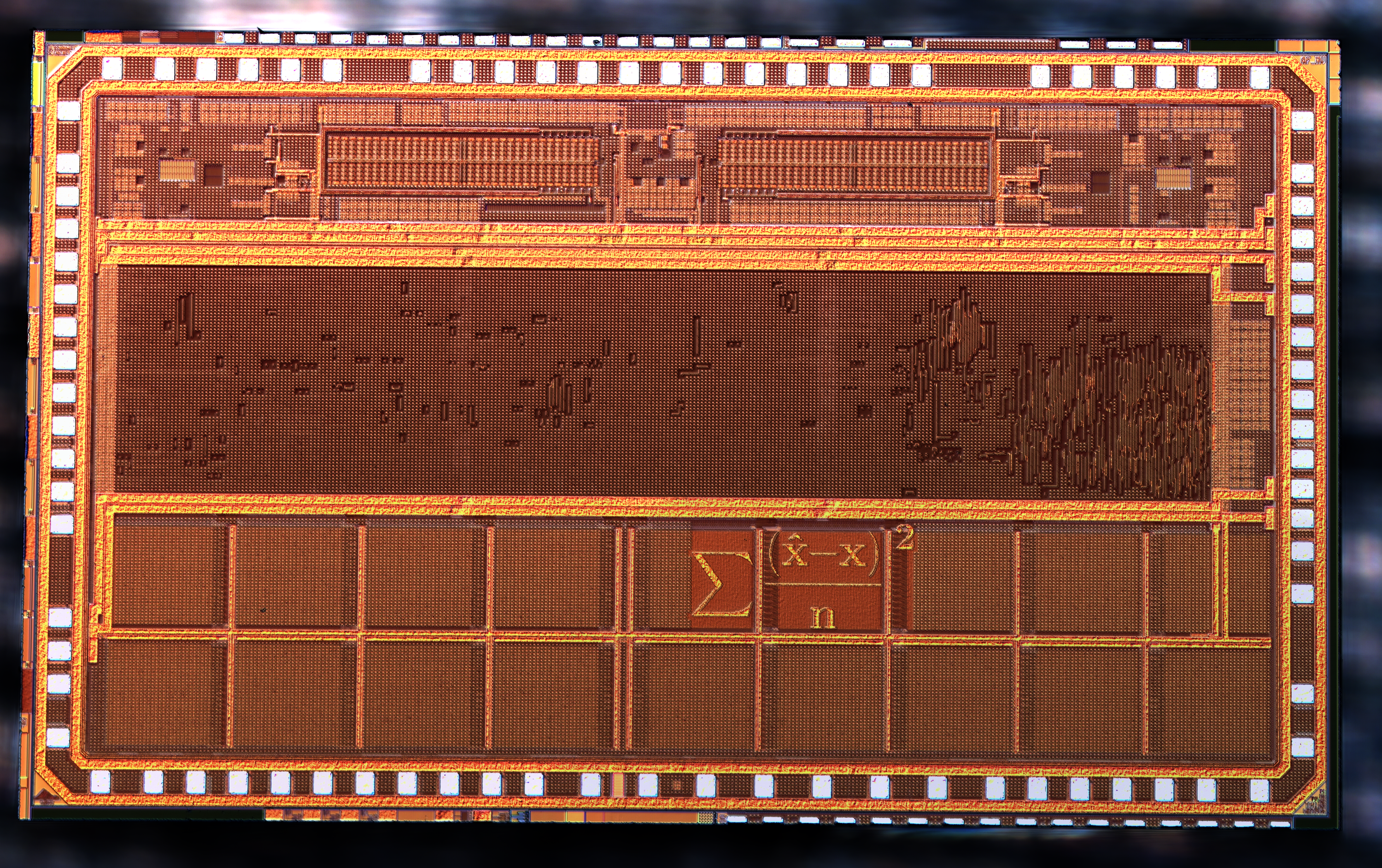

Research project

Analog Sensor Frontend with RISC-V

As part of this master's project, a RISC-V-based application-specific integrated circuit (ASIC) was developed to serve as a sensor front-end.

The purpose is to serve as a demonstration of chip design with a 180nm manufacturing process. The chip integrates a RISC-V microprocessor core with an analog front end into the IP library of the Institute of Microelectronics, Embedded Systems and Sensors (IMES).