| Studenten/-innen   | Jonas Pfister                       |

|--------------------|-------------------------------------|

| Dozenten/-innen    | Prof. Dr. Paul Zbinden              |

| Co-Betreuer/-innen | Roman Willi                         |

| Themengebiet       | Mikroelektronik                     |

| Projektpartner     | Hamilton Bonaduz AG, Rapperswil, SG |

|                    |                                     |

## Delta-Sigma ADC für 3-Phasen-Synchronmotor

## Integration eines Delta-Sigma Wandlers in ein FPGA

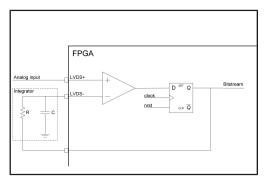

Realisation des Delta-Sigma Wandlers durch Nutzung der LVDS Eingänge

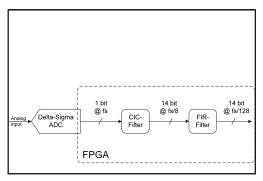

Systemübersicht über den Delta-Sigma Wandler

Ausgangslage: Die Firma HAMILTON Bonaduz AG setzt in ihren Geräten viele 3 Phasen Motoren ein, sowohl rotative wie auch lineare. Für die Regelung dieser Motoren wurde ein «Motion Controller" entwickelt. Dafür soll nun eine verbesserte Strommessung entwickelt werden. Beim aktuellen Motion Controller werden die Ströme der drei Phasen über Shunt Widerstände gemessen und mit den entsprechenden Messverstärkern aufbereitet. Die Signale werden von einem Analog-Digital Wandler gemessen, welcher sich im für die Regelung verwendeten Mikrokontroller befindet. Dieser löst mit einer Auflösung von 10 Bit auf und tastet das Signal mit einer Frequenz von 10 kHz ab. Weil dieses Verfahren nun an seine Grenzen stösst, wurden die benötigten Transformationen bereits in ein FPGA ausgelagert. Die momentan beschränkende Analog-Digital Wandlung möchte man nun ersetzen. Dazu bietet sich das bereits vorhandene FPGA an.

Ziel der Arbeit: In einem ersten Schritt soll geprüft werden, in welchem Grad ein Delta-Sigma Wandler als Teil des FPGA's realisiert werden kann. Dazu soll eine Zielhardware evaluiert und ein Testaufbau erstellt werden, für welchen anschliessend eine FPGA-Demoapplikation entwickelt wird. In einem zweiten Schritt soll das resultierende Signal mit geeigneten Filtern dezimiert und aufbereitet werden. Zum Schluss soll eine Untersuchung aufzeigen, welche Geschwindigkeiten und Auflösungen mit dem erstellten Aufbau möglich sind.

Ergebnis: Das gefundene Verfahren für die Analog-Digital Wandlung ist nicht neu. Nichts desto trotz ist es sehr elegant. Für die Delta-Sigma Modulation werden die Eigenschaften der in den meisten FPGA's vorhandenen LVDS (Low-Voltage-Differential-Signaling) Eingänge ausgenutzt. Diese werden üblicherweise zur digitalen Datenübertragung zwischen verschiedenen Chips verwendet. Zusätzlich werden pro Messkanal nur zwei externe Bauteile benötig. Der generierte Bitstream wird anschliessend durch einen Filterblock gefiltert. Dieser besteht aus zwei Stufen, einem CIC (Cascaded-Integrator-Comb) Filter und einem FIR (Finite-Impulse-Response) Tiefpass Filter. Erste Messungen haben gezeigt, dass mit diesem Delta-Sigma Wandler erster Ordnung die theoretisch mögliche Auflösung fast erreicht werden kann. Für den Einsatz bei HAMILTON wird jedoch eine höhere Genauigkeit gefordert. Mit einem Wandler zweiter Ordnung könnte dies vermutlich erreicht werden.